## CIR-V5DESF5632G

Description

DDR5 DIMM 5600MHz 32GB with ECC

| Description                                              |

|----------------------------------------------------------|

| CIR-V5DESF5632G is a 4G x 72-bit (32GB) DDR5-5600        |

| CL46 SDRAM (Synchronous DRAM), 2Rx8, memory module       |

| based on twenty 2G x 8-bit FBGA components. The SPD is   |

| programmed to JEDEC standard latency DDR5-5600 timing    |

| of 46-45-45 at 1.1V. Each 288-pin DIMM uses gold contact |

| fingers.                                                 |

Power management integrated circuit (PMIC) provides better signal integrity and more stable power. Original DRAM chips and all components are stringently tested for the highest level of compatibility, reliability, and performance.

This DDR5 ECC U-DIMM is intended for use as main memory when installed in PCs, laptops and other systems.

|  | Specifications         |                    |  |  |  |

|--|------------------------|--------------------|--|--|--|

|  | Density                | 32GB               |  |  |  |

|  | Pin Count              | 288pin             |  |  |  |

|  | Туре                   | Unbuffered         |  |  |  |

|  | Dimensions             | 133.35mm x 31.25mm |  |  |  |

|  | ECC                    | with ECC           |  |  |  |

|  | Component Config       | 2G x 8 bit         |  |  |  |

|  | Data Rate              | 5600 MHz           |  |  |  |

|  | CAS Latency            | 46                 |  |  |  |

|  | Voltage                | 1.1V               |  |  |  |

|  | PCB Layers             | 8                  |  |  |  |

|  | Operating Temp.(TCASE) | 0°C~+85°C          |  |  |  |

|  | Module Ranks           | Dual Rank          |  |  |  |

## **Features**

- JEDEC Standard 288-pin Dual In-Line Memory Module

- VDD = VDDQ = 1.1V (1.067V~1.166V)

- VPP = VDDSPD =1.8V

- Programmable /CAS Latency: 22,26,28,30,32,36,40,42,46,50

- PMIC on DIMM, nominal supply 5V, VIN\_Bulk input supply range: 4.25 V to 5.5 V

- On-die, internal, adjustable VREF generation for DQ,CA,CS

- 16n-bit prefetch

- Two independent I/O sub channels

- On-Die ECC

- SPD Hub with Thermal Sensor

- Fly-By topology

- Terminated control, command and address bus

- RoHS Compliant and Halogen free

## **Speed Grade**

| Frequency Grade Data Transfer Ra | Data Transfer Rate | CAS Latency Support |     |      | CL-tRCD-tRP |

|----------------------------------|--------------------|---------------------|-----|------|-------------|

|                                  |                    | CL40                | ТВС | CL46 |             |

| DDR5-5600                        | PC5-44800          | 4800                | TBC | 5600 | 46-45-45    |

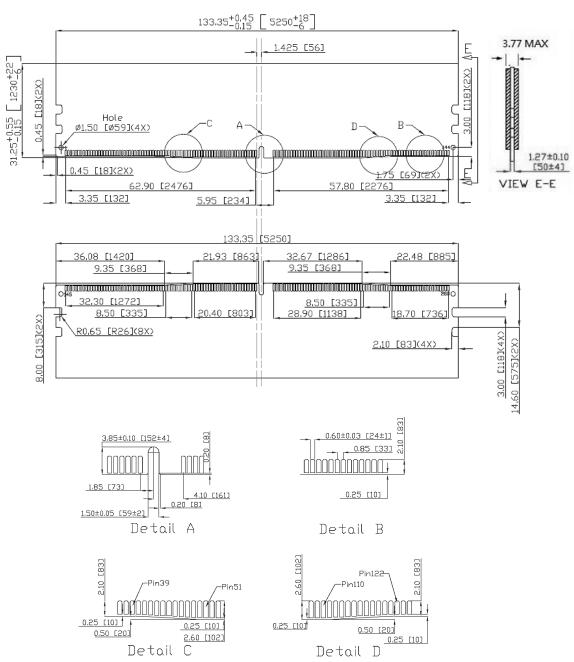

## **Package Dimensions**

Unit: mm

Tolerances: + 0.15mm unless otherwise specified